## Application Note 387 Using DS2148/348 as a Repeater

## www.maxim-ic.com

## INTRODUCTION

This application note describes the register settings for Dallas Semiconductor's DS2148 and DS21348 (E1/T1/J1 line interface units) as a repeater for T1 or E1 operation. This can be accomplished with the device in either hardware or software mode.

The receive sensitivity for these two LIUs is programmable and is as much as -36dB for T1 applications and -43dB for E1 applications.

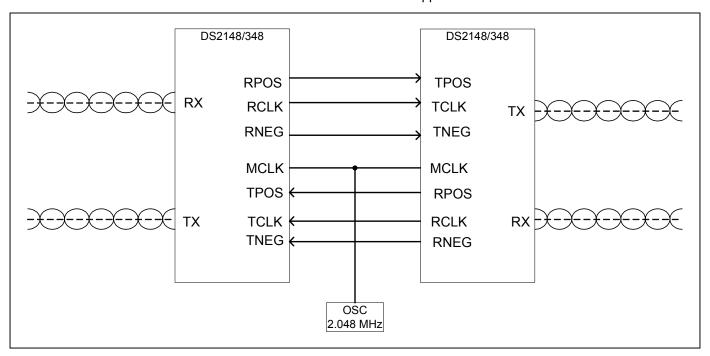

To simplify the design, it is recommended to use a 2.048MHz oscillator and use the internal register settings of the DS2148 and the DS21348 to convert the MCLK to 1.544MHz for T1 applications.

Figure 1. Typical T1/E1 Repeater Application

1 of 3 REV: 090903

The configuration settings of the DS2148 or the DS21348 in hardware mode are:

| HARDWARE MODE SETTINGS FOR T1                                        | HARDWARE MODE SETTINGS FOR E1                                                                                       |  |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| MCLK = 2.048MHz                                                      | MCLK = 2.048MHz                                                                                                     |  |

| BIS1 = 1, BIS0 = 1                                                   | BIS1 = 1, BIS0 = 1                                                                                                  |  |

| CES = 0                                                              | CES = 0                                                                                                             |  |

| DJA = 0 or 1 (application dependent)                                 | DJA = 0 or 1 (application dependent)                                                                                |  |

| HBE = 1                                                              | HBE = 1                                                                                                             |  |

| JAS = 0 or 1 (application dependent)                                 | JAS = 0 or 1 (application dependent)                                                                                |  |

| NRZE = 0                                                             | NRZE = 0                                                                                                            |  |

| TPD = 0                                                              | TPD = 0                                                                                                             |  |

| L2 = L1 = L0 = 0                                                     | L2/L1/L0 (application dependent)                                                                                    |  |

| TX1 = 0, TX0 = 0                                                     | TX1 = 0, TX0 = 0                                                                                                    |  |

| LOOP1 = 0, LOOP0 = 0                                                 | LOOP1 = 0, LOOP0 = 0                                                                                                |  |

| EGL = 1, ETS = 1 (limited long haul)<br>EGL = 0, ETS = 1 (long haul) | EGL = 0, ETS = 0 (short haul)<br>EGL = 1, ETS = 0 (long haul)                                                       |  |

| MM1 = 0, MM0 = 0                                                     | MM1 = 0, MM0 = 0                                                                                                    |  |

| RT1 = 1, RT0 = 0 (internal Rx side, $100\Omega$ enabled)             | RT1 = 0, RT0 = 1 (internal Rx side, $120\Omega$ enabled)<br>RT1 = 1, RT0 = 1 (internal Rx side, $75\Omega$ enabled) |  |

| JAMUX = 1, ETS = 1                                                   | JAMUX = 1, ETS = 0                                                                                                  |  |

The configuration settings of the DS2148 or the DS21348 in software mode are:

| SOFTWARE MODE REGISTER SETTINGS FOR T1 |                                                  | SOFTWARE MODE REGISTER SETTINGS FOR E1 |                                                                  |

|----------------------------------------|--------------------------------------------------|----------------------------------------|------------------------------------------------------------------|

| MCLK = 2.048MHz                        |                                                  | MCLK = 2.048MHz                        |                                                                  |

| CCR1 (00H)                             | CCR1.7 = 1                                       | CCR1 (00H)                             | CCR1.7 = 0                                                       |

|                                        | CCR1.6 = 0                                       |                                        | CCR1.6 = 0                                                       |

|                                        | CCR1.3 = 1                                       |                                        | CCR1.3 = 1                                                       |

|                                        | CCR1.1 = 1                                       |                                        | CCR1.1 = 1                                                       |

| CCR2 (01H)                             | CCR2.3 = 1                                       | CCR2 (01H)                             | CCR2.3 = 1                                                       |

|                                        | CCR2.2 = 1                                       |                                        | CCR2.2 = 1                                                       |

|                                        | CCR2.1 = 0                                       |                                        | CCR2.1 = 0                                                       |

|                                        | CCR2.0 = 0                                       |                                        | CCR2.0 = 0                                                       |

| CCR4 (03H)                             | CCR4.7 = CCR4.6 = CCR4.5 = 0                     | CCR4 (03H)                             | CCR4.7, CCR4.6, and CCR4.5 (application dependent)               |

|                                        | CCR4.1 (application dependent)                   |                                        | CCR4.1 (application dependent)                                   |

|                                        | CCR4.0 = 0                                       |                                        | CCR4.0 = 0                                                       |

| CCR5 (04H) CCR5.1 = 1, 0               |                                                  | CCR5 (04H)                             | CCR5.5 = 0, CCR5.4 = 0                                           |

|                                        | CCR5.5 = 0, CCR5.4 = 0<br>CCR5.1 = 1, CCR5.0 = 0 |                                        | CCR5.1 = 0, CCR5.0 = 1 (internal RX side, $120\Omega$ enabled)   |

|                                        | (internal Rx side, 100 $\Omega$ enabled)         |                                        | CCR5.1 = 1, CCR5.0 = 1<br>(internal Rx side, $75\Omega$ enabled) |